~~~ La versione in italiano inizia subito dopo la versione in inglese ~~~

ENGLISH

21-12-2024 - Computer science basics - Computer, the system bus (2) [EN]-[IT]

With this post I would like to give a brief instruction on the topic mentioned in the subject

(code notes: X_16)

Computer, the system bus (2)

OPERATION AND CYCLES

In terms of bus operation, as already mentioned, the operations performed on the bus are transfers of information between master and slave. Furthermore, each transfer performed on the bus corresponds to a bus cycle. These cycles can be classified as:

⎯ reading a memory word;

⎯ writing a memory word;

⎯ reading an I/O register;

⎯ writing an I/O register;

⎯ rest (condition in which the bus is not used).

Keep in mind that a single read or write operation can also develop over multiple bus cycles. In particular, a transfer cycle can be broken down into the following phases:

⎯ selection: the master selects the slave involved in the transfer, indicating its address, the type of element (whether memory or I/O device) and the direction (whether reading or writing);

⎯ possible waiting: if the slave involved is slow and requires a longer access time than normal bus cycles, this waiting condition involves the insertion of wait states;

⎯ data transfer: the slave locally stores the information emitted by the master;

⎯ conclusion: all the signals are neatly returned to the rest state.

When we talk about the control signals next also mention the Bus Acknowledge.

The Bus Acknowledge (often abbreviated as "BTA" or "Acknowledge Signal") is a signal used in digital systems and communication protocols to confirm that a device or component has received a request and/or has completed an operation. control signals

Here are some information pills regarding the subject in question.

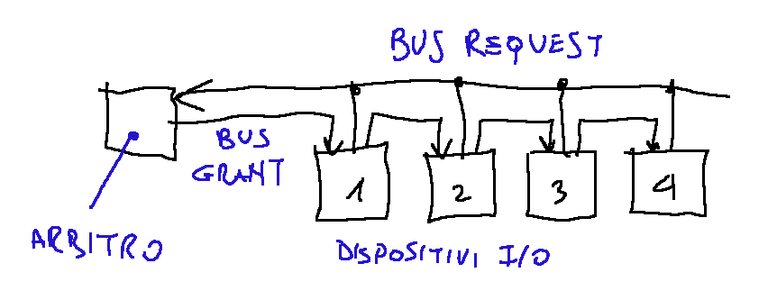

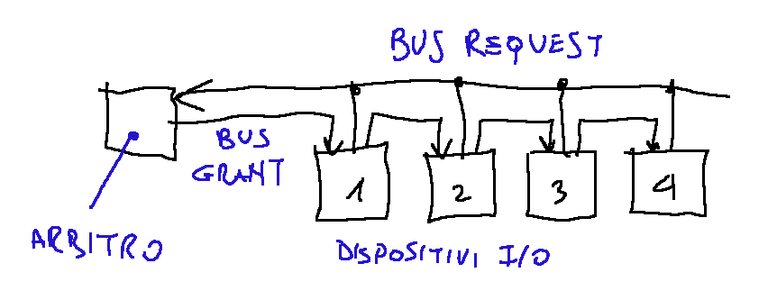

1-Bus Request and Bus Grant

The Bus Request and Bus Grant lines are the lines for requesting the transfer of control and the lines for confirming the transfer of control, respectively.

2-Centralized Arbitration

In the centralized arbitration mechanism, the unit in contact with the arbiter has a higher priority than the unit far from the arbiter

3-Definition of Cycle

In terms of bus operation, a cycle is defined as one transfer of information performed on the bus.

4-Transfer cycle composition

A transfer cycle is composed of selection, possible waiting, data transfer, conclusion

5-handshake

The term handshake indicates the dialogue between master and slave for the management of operations

6-asynchronous mode timing

Asynchronous mode bus timing allows efficient use of cycles

7-synchronous mode bus timing

In synchronous mode bus timing, the clock signal marks the passage from one bus cycle to the next cycle

8-MREQ

The MREQ signal made available by the control bus indicates that the master is requesting an access operation from the memory

9-Bus Acknowledge

In the centralized arbitration mechanism, the Bus Acknowledge is a line of activity control from the units that improves the efficiency of the arbitration

10-distributed arbitration

In the distributed arbitration mechanism, a BUS request line is provided for each unit

Conclusions

The controls performed by the bus ensure the correct transmission of data, addresses and control signals, contributing to the stability, efficiency and reliability of the system. The main aspects of the system bus controls are: Synchronization and Arbitration, Data Integrity, Error Management, Communication Efficiency, Compatibility and Scalability. We can say in general that the controls performed by the system bus are fundamental for the coordinated and error-free operation of a computer.

Question

I find that the operation of the controls of a system bus also teaches how to work. When we do a work activity, the control guarantees efficiency, what do you think?

[ITALIAN]

21-12-2024 - Basi di informatica - Calcolatore, il bus di sistema (2) [EN]-[IT]

Con questo post vorrei dare una breve istruzione a riguardo dell’argomento citato in oggetto

(code notes: X_16)

Calcolatore, il bus di sistema (2)

FUNZIONAMENTO E CICLI

In termini di funzionamento del bus, come già detto, le operazioni eseguite sul bus sono trasferimenti di informazioni tra master e slave. Inoltre, ogni trasferimento compiuto sul bus corrisponde a un ciclo di bus. Questi cicli sono classificabili in:

⎯ lettura d’una parola di memoria;

⎯ scrittura d’una parola di memoria;

⎯ lettura d’un registro di I/O;

⎯ scrittura d’un registro di I/O;

⎯ riposo (condizione in cui il bus non viene utilizzato).

Si tenga presente che una singola operazione di lettura o scrittura può anche svilupparsi su più cicli di bus. In particolare, un ciclo di trasferimento può essere scomposto nelle fasi seguenti:

⎯ selezione: il master seleziona lo slave coinvolto dal trasferimento, indicandone l’indirizzo, il tipo d’elemento (se memoria o dispositivo I/O) e il verso (se lettura o scrittura);

⎯ eventuale attesa: se lo slave coinvolto è lento e necessita di un tempo d’accesso maggiore rispetto ai normali cicli di bus, questa condizione di attesa comporta l’inserimento di stati di wait;

⎯ trasferimento dei dati: lo slave memorizza localmente l’informazione emessa dal master;

⎯ conclusione: tutti i segnali sono ordinatamente riportati nello stato di riposo.

Quando parliamo dei segnali di controllo prossimo anche nominare il Bus Acknowledge.

Il Bus Acknowledge (spesso abbreviato come "BTA" o "Acknowledge Signal") è un segnale utilizzato nei sistemi digitali e nei protocolli di comunicazione per confermare che un dispositivo o un componente ha ricevuto una richiesta e/o ha completato un'operazione. segnali di controllo

Qui di seguito alcune pillole di informazioni a riguardo dell’argomento in oggetto.

1-Bus Request e Bus Grant

Le linee Bus Request e Bus Grant sono rispettivamente le linee di richiesta di cessione del controllo e le linee di conferma di cessione del controllo.

2-Arbitraggio centralizzato

Nel meccanismo di arbitraggio centralizzato l’unità a contatto con l’arbitro ha priorità maggiore rispetto all'unità lontana dall'arbitro

3-Definizione di ciclo

In termini di funzionamento del bus, un ciclo è definito come un trasferimento di informazioni compiuto sul bus.

4-Composizione del ciclo di trasferimento

Un ciclo di trasferimento è composto da selezione, eventuale attesa, trasferimento dati, conclusione

5-handshake

Il termine handshake indica il colloquio tra master e slave per la gestione delle operazioni

6-temporizzazione in modalità asincrona

La temporizzazione del bus in modalità asincrona consente un uso efficiente dei cicli

7-temporizzazione del bus in modalità sincrona

Nella temporizzazione del bus in modalità sincrona, il segnale di clock scandisce il passaggio da un ciclo di bus al ciclo successivo

8-MREQ

Il segnale MREQ messo a disposizione dal bus di controllo indica che il master richiede alla memoria un’operazione d’accesso

9-Bus Acknowledge

Nel meccanismo di arbitraggio centralizzato, il Bus Acknowledge è una linea di controllo attività dalle unità che migliora l’efficienza dell’arbitraggio

10-arbitraggio distribuito

Nel meccanismo di arbitraggio distribuito è prevista una linea di richiesta BUS per ogni unità

Conclusioni

I controlli effettuati dal bus garantiscono la corretta trasmissione di dati, indirizzi e segnali di controllo, contribuendo alla stabilità, all'efficienza e all'affidabilità del sistema. I principali aspetti dei controlli del bus di sistema sono: Sincronizzazione e Arbitraggio, Integrità dei Dati, Gestione degli Errori, Efficienza della Comunicazione, Compatibilità e Scalabilità. Possiamo dire in generale che i controlli effettuati dal bus di sistema sono fondamentali per il funzionamento coordinato e privo di errori di un calcolatore.

Domanda

Io trovo che il funzionamento dei controlli di un bus di sistema insegni anche a lavorare. Quando facciamo un'attività lavorativa, il controllo garantisce efficienza, voi come la pensate?

THE END